EP1C4F324C7N FPGA : 데이터 시트, 기능, 프로그래밍 및 사양

이 안내서는 인텔이 만든 FPGA 칩의 유형 인 EP1C4F324C7N에 관한 것입니다.강력한 성과가 필요하지만 예산 내에서 유지 해야하는 프로젝트에 좋습니다.이 기사에서는이 칩이 수행 할 수있는 작업, 작동 방식, 사용 위치 및 프로그래밍 방법을 배웁니다.자동차, 공장 또는 홈 장치 용 전자 장치에서 일하든이 가이드는 EP1C4F324C7N이 왜 똑똑하고 유연한 선택인지 이해하는 데 도움이됩니다.목록

EP1C4F324C7N 개요

그만큼 EP1C4F324C7N 인텔의 Cyclone® FPGA 시리즈의 일부이며, 성능의 균형과 저렴한 비용이 필요한 비용 효율적인 응용 프로그램을 위해 특별히 설계되었습니다.이 FPGA에는 4,000 개의 논리 요소와 400 개의 논리 배열 블록 (Labs)이있어 적당한 복잡성 설계에 대한 강력한 기능을 제공합니다.여기에는 총 RAM 76.5 킬로 비트가 포함되어 있으며 최대 249 개의 I/O 핀을 지원하므로 다양한 인터페이스 요구 사항에 따라 매우 다양합니다.EP1C4F324C7N은 최대 320MHz의 주파수 및 공급 전압 범위가 1.425V ~ 1.575V의 주파수에서 작동합니다.LVTTL, LVCMOS, SSTL-2 및 SSTL-3과 같은 광범위한 I/O 표준을 지원하며 DDR SDRAM과 같은 외부 메모리 유형과 호환되어 디지털 신호 처리, 내장 컴퓨팅 및 자동화 시스템에서 유용성을 향상시킵니다.

신뢰할 수있는 기술로 운영을 원활하게 운영하려는 경우이 FPGA의 대량 순서를 우리와 함께 제공하면 프로젝트에 필요한 가용성과 일관성을 얻을 수 있습니다.

EP1C4F324C7N CAD 모델

EP1C4F324C7N 기호

EP1C4F324C7N 발자국

EP1C4F324C7N 3D 모델

EP1C4F324C7N 기능

• 논리 요소: FPGA에는 복잡한 논리 회로와 디지털 기능을 효율적으로 구현할 수있는 4,000 개의 논리 요소가 포함되어 있습니다.

• 로직 어레이 블록 (실험실): FPGA 아키텍처의 기본 빌딩 블록 인 400 개의 실험실이 포함되어있어 다목적 디지털 논리 구성의 설계를 용이하게합니다.

• 총 RAM 비트: FPGA에는 76.5 킬로 비트의 임베디드 RAM이 장착되어 고속 데이터 처리 및 스토리지를위한 온칩 메모리 리소스를 제공합니다.

• I/O 핀 수: 249 명의 사용자 구성 가능한 I/O 핀을 사용하여 EP1C4F324C7N은 다양한 신호 표준 및 전자 구성 요소에 적응할 수있는 다양한 인터페이스 옵션을 지원합니다.

• 작동 주파수: 최대 320MHz의 주파수에서 작동하여 고속 계산 작업 및 프로세스를 효율적으로 처리 할 수 있습니다.

• 공급 전압:이 장치는 1.425V ~ 1.575V의 공급 전압 범위 내에서 작동하여 다양한 응용 분야에서 유연하고 안정적인 전력 관리를 보장합니다.

• 위상 잠금 루프 (PLL): 타이밍에 민감한 애플리케이션을위한 정확한 클럭 관리를위한 위상 잠금 루프가 특징입니다.

• 여러 I/O 표준에 대한 지원: FPGA는 LVTTL, LVCMOS, SSTL-2 및 SSTL-3과 같은 다양한 I/O 표준을 지원하여 광범위한 전자 구성 요소 및 시스템과의 호환성을 향상시킵니다.

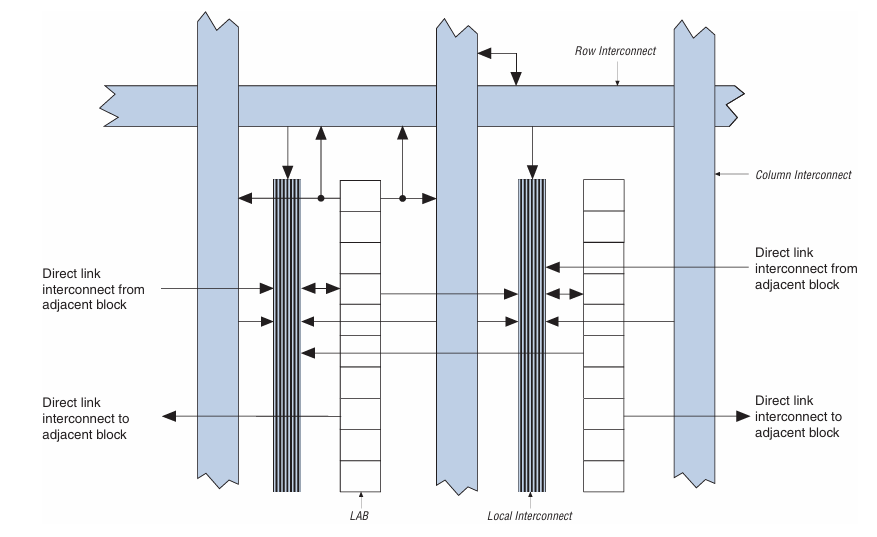

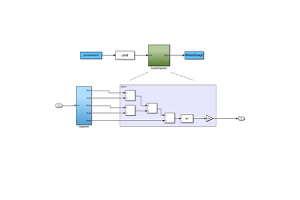

EP1C4F324C7N 블록 다이어그램

다이어그램은 FPGA 내의 상호 연결 구조를 보여줍니다. EP1C4F324C7N Altera Cyclone 시리즈의 장치.이 레이아웃의 핵심은 다음과 같습니다 논리 배열 블록 (Labs)는 사용자 로직 함수 구현을 담당하는 논리 요소 클러스터를 포함하는 수직으로 정렬 된 모듈입니다.각 실험실은 직접 링크 상호 연결을 통해 인근 실험실에 연결되어 고속 통신 및 신호 전파 지연을 최소화 할 수 있습니다.이러한 직접 링크는 더 넓은 라우팅 리소스를 소비하지 않고 인접한 로직 블록 사이에 효율적이고 현지화 된 데이터 전송을 제공합니다.

실험실을 둘러싼 두 가지 주요 유형의 글로벌 상호 연결이 있습니다. 행 상호 연결 그리고 열 상호 연결.이 넓은 파란색 라인은 라우팅 고속도로 역할을하여 신호가 FPGA 직물의 더 큰 부분을 가로 질러 가로 질 수 있습니다.행은 상호 연결되어 수평으로 실행되는 반면 열은 상호 연결되어 수직으로 실행됩니다.그들은 먼 로직 블록 사이의 연결을 용이하게하고 입력/출력 요소 또는 칩 전체에 배치 된 기타 기능 단위와의 인터페이스를 촉진합니다.

로컬 인터커넥트는 실험실 사이에 위치하며 실험실과 글로벌 상호 연결을 연결하는 스위칭 패브릭 역할을합니다.로직 블록은 직접 및 글로벌 상호 연결 모두에서 신호에 액세스 할 수 있습니다.직접, 로컬, 행 및 열 경로를 결합한이 라우팅 계층 구조는 EP1C4F324C7N FPGA 내에서 성능 및 논리 활용을 최적화하는 신호 분포에 유연하고 확장 가능한 접근 방식을 제공합니다.

EP1C4F324C7N 사양

|

유형 |

매개 변수 |

|

제조업체 |

Altera/Intel |

|

시리즈 |

사이클론 ® |

|

포장 |

쟁반 |

|

부품 상태 |

쓸모없는 |

|

실험실/CLBS 수 |

400 |

|

논리 요소/세포 수 |

4000 |

|

총 RAM 비트 |

78,336 |

|

I/O의 수 |

249 |

|

전압 - 공급 |

1.425V ~ 1.575V |

|

장착 유형 |

표면 마운트 |

|

작동 온도 |

0 ° C ~ 85 ° C (TJ) |

|

패키지 / 케이스 |

324-BGA |

|

공급 업체 장치 패키지 |

324-FBGA (19x19) |

|

기본 제품 번호 |

EP1C4 |

EP1C4F324C7N 응용 프로그램

네트워킹 장비

EP1C4F324C7N은 스위치, 라우터 및 모뎀과 같은 네트워킹 장치에서 사용하기에 매우 적합합니다.데이터 트래픽을 효율적으로 관리하여 처리량을 개선하고 고성능 네트워크 운영을 유지하기위한 대기 시간을 줄입니다.

산업 자동화

산업 자동화 분야 에서이 FPGA는 기계 및 로봇 시스템을 제어하는 데 사용될 수 있습니다.복잡한 알고리즘을 처리하는 능력은 제어 및 모니터링을 신속하게 만들어 제조 환경에서 생산성과 안전성을 향상시킵니다.

소비자 전자 장치

EP1C4F324C7N은 소비자 전자 제품, 특히 고해상도 디스플레이를 구동하고 스마트 TV 및 고급 홈 자동화 시스템과 같은 장치에서 대화식 인터페이스를 관리하는 데 응용 프로그램을 찾습니다.강력한 처리 기능은 매끄럽고 반응적인 경험을 보장합니다.

자동차 시스템

자동차 애플리케이션 내 에서이 FPGA는 ADA (Advanced Driver-Asistance Systems) 및 차량 내 인포테인먼트 시스템의 기능에 기여합니다.현대 차량의 안전 및 엔터테인먼트 기능을위한 처리 및 의사 결정을 지원합니다.

항공 우주 및 방어

FPGA는 항공 우주 및 방어 부문에도 적용되며, 여기서 레이더 및 통신 시스템의 신호 및 이미지 처리 작업을 처리합니다.극한 조건에서 높은 신뢰성과 운영 능력은 군사 및 항공 우주 응용에 이상적입니다.

EP1C4F324C7N 유사한 부분

EP1C4F324C7N 프로그래밍 단계

1. 디자인 생성: vhdl 또는 verilog와 같은 하드웨어 설명 언어를 사용하여 디자인을 작성하여 시작하십시오.이 코드는 하드웨어 구현의 논리적 구조와 기능을 정의합니다.FPGA가 예상대로 작동하는지 확인하기 위해 하드웨어 아이디어를 HDL로 정확하게 번역하는 것이 중요합니다.하드웨어 구현을 진행하기 전에 시뮬레이션 소프트웨어를 사용하여 HDL 코드를 시뮬레이션하십시오.이 단계는 가상 환경에서 디자인의 논리와 기능을 테스트하여 개발 프로세스 초기에 오류를 식별하고 수정할 수 있습니다.

2. 컴파일 및 합성 : Altera의 Quartus II 소프트웨어를 사용하여 HDL 코드를 컴파일하고 합성하십시오.컴파일은 HDL을 넷리스트로 변환하는데, 디자인을 논리 요소 및 라우팅 리소스에 매핑하는 FPGA 하드웨어에 대한 일반적인 설명입니다.Quartus II 워크 플로의 일부인 피팅 프로세스에는 FPGA 내에 디자인을 배치하고 라우팅하는 것이 포함됩니다.그것은 로직 요소의 배치와 성능 요구 사항을 충족시키고 리소스 사용량을 최소화하기 위해 연결 라우팅을 최적화합니다.

3. PIN 과제: Quartus II의 핀 플래너를 사용하면 FPGA의 특정 핀을 HDL 코드에 정의 된 입력 및 출력에 할당 할 수 있습니다.적절한 핀 할당은 시스템의 다른 하드웨어 구성 요소와 FPGA의 물리적 연결 및 상호 작용에 좋습니다.

4. 타이밍 분석: TimeQuest 타이밍 분석기를 사용하여 설계가 타이밍 요구 사항을 충족하는지 확인하십시오.이 도구는 설정 및 보류 시간 및 전체 타이밍 성능을 확인하여 데이터 손상 및 시스템 불안정성과 같은 문제를 방지합니다.

5. 프로그래밍 파일 생성: 디자인을 컴파일, 합성 및 타이밍을 위해 검증 한 후 쿼터 II 내의 어셈블러 도구를 사용하여 프로그래밍 파일을 생성하십시오.일반적으로 .sof (sram 객체 파일) 또는 .pof (programmable 객체 파일) 확장자가있는이 파일에는 fpga의 구성 데이터가 포함됩니다.

6. 장치 프로그래밍: USB 블래스터와 같은 JTAG 인터페이스를 사용하여 FPGA 보드를 컴퓨터에 연결하십시오.이 인터페이스는 PC에서 FPGA로 프로그래밍 파일을 전송하는 데 사용됩니다.Quartus II 프로그래머 도구를 열어 프로그래밍 파일을 FPGA로로드하고 전송하십시오.이 단계는 디자인으로 FPGA를 구성하여 기본적으로 원하는 기능을 수행하도록 장치를 "프로그래밍"합니다.

7. 검증: FPGA가 프로그래밍되면 기능 테스트를 수행하여 설계 사양에 따라 FPGA가 올바르게 작동하는지 확인하십시오.이 테스트에는 실험실 환경에서 테스트 케이스를 실행하고 인터페이스 작업을 확인하고 FPGA가 다른 하드웨어 구성 요소와 올바르게 상호 작용하는지 확인할 수 있습니다.

EP1C4F324C7N 장점

유연성과 재구성 가능성

EP1C4F324C7N은 마이크로 컨트롤러 및 ASIC에 비해 비교할 수없는 유연성을 제공하며, 이는 일단 제조 된 기능에 고정되어 있습니다.이 FPGA는 시간이 지남에 따라 진화하는 응용 프로그램의 새로운 요구 사항 또는 시스템 설계 변경에 적응하도록 재 프로그래밍 할 수 있습니다.이 재구성 가능성을 통해 하드웨어를 교체하지 않고 시스템을 업데이트하여 비용과 개발 시간을 줄일 수 있습니다.

병렬 처리 기능

EP1C4F324C7N은 여러 작업을 동시에 실행할 수있는 능력으로 고성능 컴퓨팅이 필요한 환경에서 뛰어납니다.이 병렬 처리 기능은 순차적으로 작동하는 전통적인 마이크로 컨트롤러에 비해 이점이므로 FPGA는 디지털 신호 처리, 비디오 처리 및 복잡한 제어 시스템과 같은 집중 애플리케이션에 더 적합합니다.

사용자 정의 하드웨어 구현

FPGA를 사용하면 사용자의 운영 요구에 맞게 맞춤화 된 맞춤형 하드웨어 로직 설계를 가능하게합니다.이는 EP1C4F324C7N이 표준 프로세서 나 ASIC보다 특정 작업을보다 효율적으로 수행하도록 최적화되어 특수 애플리케이션에 우수한 성능 및 전력 효율성을 제공 할 수 있음을 의미합니다.

저용량에서 중간 중반 생산에 대한 비용 효율성

생산량으로 인해 ASIC 개발 비용이 높은 프로젝트의 경우 EP1C4F324C7N은 비용 효율적인 대안을 제시합니다.ASIC 설계 및 제조에 필요한 상당한 선결제 투자없이 맞춤형 하드웨어의 이점을 제공하여 프로토 타입, 중소형 프로젝트 또는 전문 산업 응용 프로그램에 이상적입니다.

통합 및 공간 효율성

여러 기능과 구성 요소를 단일 FPGA 칩에 통합하는 기능은 EP1C4F324C7N을 공간 제한 응용 분야에서 매우 가치있게 만듭니다.이 통합은 더 작고 컴팩트 한 장치 설계로 이어지고 휴대용 전자 제품, 자동차 응용 프로그램 및 공간 효율이 필요한 기타 시나리오가 크게 이어집니다.

EP1C4F324C7N 포장 치수

• 패키지 유형: 324 핀 파인 피치 볼 그리드 어레이 (FBGA)

• 패키지 크기 (길이 x 너비) : 19 mm x 19 mm

• 최대 좌석 높이: 3.5 mm

• 터미널 피치: 1 mm

EP1C4F324C7N 제조업체

EP1C4F324C7N은 FPGA (Field Programmable Gate 어레이)입니다. 인텔Altera의 인수 후.Intel 's Cyclone® 시리즈의 일환 으로이 FPGA는 인텔의 광범위한 통합 기술 솔루션 포트폴리오의 세그먼트를 나타냅니다.반도체 산업의 리더 인 Intel은 고급 제조 기술과 광범위한 지원을 통합하여 EP1C4F324C7N을 포함하여 강력한 FPGA 솔루션을 제공합니다.이 FPGA는 다양한 기술 요구를 충족시키는 고성능 컴퓨팅 구성 요소를 제공하겠다는 Intel의 약속을 강조합니다.

결론

Custom Control Logic을 개발하거나 고속 통신 시스템 구축 또는 전문화 된 디지털 기능을 개발하든 EP1C4F324C7N FPGA는 성능, 유연성 및 비용의 최적 균형을 제공합니다.광범위한 I/O 호환성, 통합 메모리 및 효율적인 재구성 성을 통해 광범위한 최신 응용 분야에서 확장 가능하고 공간 효율적인 설계를 지원합니다.Intel의 업계 최고의 지원에 의해 뒷받침되는이 FPGA는 저용량 및 중반 배포 모두에서 강력한 프로그래밍 가능한 논리를 찾기위한 신뢰할 수 있고 적응 가능한 솔루션으로 남아 있습니다.

데이터 시트 PDF

EP1C4F324C7N 데이터 시트 :

Mult Dev Dessicant CHG 19/7 월/2019.pdf

멀티 시리즈 소프트웨어 CHG 26/3 월/2020.pdf

우리에 대해

ALLELCO LIMITED

더 많은 것을 읽으십시오

빠른 문의

문의를 보내 주시면 즉시 응답하겠습니다.

자주 묻는 질문 [FAQ]

1. EP1C4F324C7N을 DDR 또는 SDRAM과 함께 사용할 수 있습니까?

예,이 FPGA는 다중 표준 I/O 지원 덕분에 DDR SDRAM을 포함한 외부 메모리 유형을 지원합니다.그러나 PCB 레이아웃은 고속 메모리 인터페이스에 대한 엄격한 타이밍 및 임피던스 지침을 준수해야합니다.

2. EP1C4F324C7N의 일반적인 전력 요구 사항은 무엇입니까?

이 장치는 I/O 표준에 추가 전압이 필요한 1.425V ~ 1.575V 코어 전압으로 작동합니다.정확한 전력 계획을 위해 쿼터 내에서 Intel의 PowerPlay Power Analyzer를 사용하여 설계에 따라 소비를 추정하십시오.

3. EP1C4F324C7N ROHS는 준수하고 무연입니까?

예, EP1C4F324C7N은 ROHS 지침을 준수하며 무연 패키지로 제공됩니다.이로 인해 녹색 전자 제품 인증이 필요한 환경 규제 시장 및 응용 프로그램에 적합합니다.

4. EP1C4F324C7N에 디자인을 컴파일하고 프로그래밍하는 데 얼마나 걸립니까?

적당한 복잡성 설계의 경우 컴파일 및 프로그래밍은 일반적으로 PC의 성능에 따라 3 ~ 5 분이 걸립니다.설계에 타이밍 제약 조건이 필요한 경우 타이밍 분석 및 핀 할당이 프로세스를 확장 할 수 있습니다.

5. EP1C4F324C7N을 프로그래밍하기 위해 특별한 도구가 필요합니까?

무료 Lite 에디션과 USB 블래스터 또는 호환 JTAG 프로그래머로 제공되는 Intel의 Quartus II 소프트웨어가 필요합니다.이 도구를 사용하면 디자인을 컴파일하고 프로그래밍 파일을 생성 한 후 FPGA에 업로드 할 수 있습니다.

GC5330IZEV 디지털 신호 프로세서 : 기능, 응용 프로그램, 대안 및 사양

4월1일에서

0402 저항에 대한 완전한 가이드 : 사양, 응용 및 납땜 기술

4월1일에서

인기있는 게시물

-

복잡한 명령 세트 컴퓨터 : 컴퓨터를 어떻게 변경 했습니까?

4월18일에서 147760

-

USB-C 핀아웃 및 기능

4월18일에서 111979

-

Xilinx Unified Simulation Primitive 사용 : FPGA 설계 및 시뮬레이션에 대한 포괄적 인 안내서

4월18일에서 111351

-

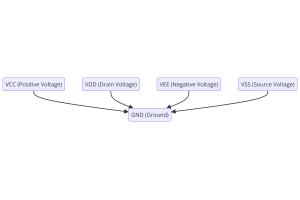

전자 장치의 전원 공급 장치 전압: VCC, VDD, VEE, VSS 및 GND의 의미

4월18일에서 83743

-

RJ45 커넥터 가이드 : 핀아웃, 배선, 케이블 유형 및 사용

1월1일에서 79529

-

현대 전기 시스템에서 와이어 컬러 코드에 대한 궁극적 인 가이드

전기 시스템이 색상을 사용하는 방식은 외관만을위한 것이 아닙니다.각 와이어 색상은 이제 특정 기능을 나타내므로 설치 및 유지 보수 중에 전기 부품을보다 쉽게 식별하고 처리 할 수 있습니다.이는 운영 프로세스를 가속화 할뿐만 아니라 실수의 기회를 줄이고 사용자와 기술자 모두가 안전하게 지내도록 도와줍니다.이 기사는 와이어 컬러 코드의 중요성, 안...1월1일에서 66943

-

퍼지 밸브 가이드 : 최적의 엔진 성능을위한 기능, 증상, 테스트 및 교체

퍼지 밸브는 대기로 빠져 나가기 전에 연료 증기를 관리함으로써 공기를 깨끗하게 유지하는 데 도움이되는 자동차 시스템의 핵심 부분입니다.이것은 오염을 줄임으로써 환경에 도움이 될뿐만 아니라 자동차를 개선하고 연료를보다 효율적으로 사용하게합니다.이 기사에서는 퍼지 밸브가 작동하는 방식, 유형 및 제대로 작동하는지 확인하는 방법을 포함하여 Purge 밸브에...1월1일에서 63086

-

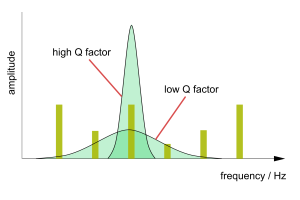

품질 (Q) 요인 : 방정식 및 응용

RF (Radio Frequencies)를 사용하는 전자 시스템에서 인덕터와 공진기가 얼마나 잘 작동하는지 확인할 때 품질 요소 또는 'Q'가 중요합니다.'Q'는 회로가 에너지 손실을 최소화하고 시스템이 주요 주파수 주변에서 처리 할 수있는 주파수 범위에 얼마나 잘 영향을 미치는지 측정합니다.인덕터, 커패시터 및 조정 된 회로가있는 시스템에서 더 높은...1월1일에서 63025

-

최대 전력 전송 정리로 피크 성능을 달성합니다

최대 전력 전송 정리는 배터리 또는 발전기와 같은 소스의 에너지가 연결 하중으로 흐르는 방법을 설명합니다.부하가 가장 많은 전력을받는 정확한 조건을 보여줍니다.이 기사는 정리의 의미, DC 및 AC 회로에서 작동하는 방식, 배후의 증거, 실제 응용 프로그램 및 장점 및 단점을 다룹니다.결국,이 원리가 태양 전지판, 라디오, 스피커 및 무선 충전과 같은...1월1일에서 54092

-

A23 배터리 사양 및 호환성

A23 배터리는 전압이 높은 작은 실린더 모양의 배터리입니다.23A, 23AE 또는 MN21이라고도하는 경우에도 12 볼트로 작동하며 AA 또는 AAA 배터리보다 훨씬 높습니다.특별한 디자인은 작지만 강력한 전원이 필요한 가제트에 적합합니다.이 기사는 A23 배터리의 기능, 성능 및 사용을 살펴 봅니다.다른 브랜드와 기타 일반적인 배터...1월1일에서 52167